#### **Use Authorization**

In presenting this dissertation in partial fulfillment of the requirements for an advanced degree at Idaho State University, I agree that the Library shall make it freely available for inspection. I further state that permission to download and/or print my dissertation for scholarly purposes may be granted by the Dean of the Graduate School, Dean of my academic division, or by the University Librarian. It is understood that any copying or publication of this dissertation for financial gain shall not be allowed without my written permission.

Signature\_\_\_\_\_

Date \_\_\_\_\_

# GPU Oriented Approach to Finite Element Multiphysics Simulation

By

Dawid L. Krol

A Dissertation submitted in partial fulfillment of the Requirement for the degree of

Doctor of Philosophy in Engineering and Applied Science

**IDAHO STATE UNIVERSITY**

May 2015

To the Graduate Faculty:

The members of the committee appointed to examine the dissertation of DAWID KROL find it satisfactory and recommend that it be accepted.

Dr. Steve Chiu, Major Advisor

Dr. Dawid Zydek, Committee Member

Dr. Eugene Stuffle, Committee Member

Dr. Hossein Mousavinezhad, Committee Member

Dr. Jason Harris, Graduate Faculty Representative

### Dedication

I dedicate this thesis to my beloved wife Joanna Bieganska. Back in 2012 she decided to go through this wonderful but also demanding journey with me asking for nothing in return. She is the most the most charming and kind person I have ever meet. She believe in me unconditionally more than anyone else including myself. Thanks to her support and help in almost every area on my life I was able to complete the Ph.D. program and to finish the dissertation – I am sure that would not be able to do that without Joanna.

I would also like to extend the dedication to my parents – Grazyna and Kazimierz Krol – for their support, helping hand, and weekly Sunday Skype calls. Knowing that you have a place that you can call *Home* and to which you can come back no matter what happens is one of the most comforting thing on Earth. I would also like to thank my parents for being a *role models* for me a long before I knew what it means.

### Acknowledgement

Firstly I would like to thank Dr. Dawid Zydek – my first advisor at Idaho State University and a person that made my Ph.D. program possible. Throughout all of these years, and even after Dr. Zydek decided to follow other career path, he always had time to answer my questions regarding research, address my concerns, or simply have a casual conversation. Dr. Zydek has extraordinary and positive influence on my research and thesis; he helped me greatly with all my publications. Every conversation we made was very motivating and encouraging to make further effort. Aside from academia, Dr. Zydek helped me a lot with making first step, or actually first few hundreds steps, in United States of America. I will never forget how much Dr. Zydek did for me and I will be always thankful for that and for his friendship.

I would also like to thank Dr. Steve Chiu who agreed to be my advisor for final year of program. I am sure it was not an easy decision to take a responsibility for student in final stage of research. Without his help I would never be able finish Ph.D. program. I am also very grateful for all the time Dr. Chiu spent on answering my countless emails, helping hand in number of academia and non-academia situations, and valuable advices regarding my future career in United States of America. At last but not at least I want to express my gratitude for great influence on the direction and form of my research.

A special thanks Committee Members (listed in alphabetical order) for their time and commitment: Dr. Jason Harris, Dr. Hossein Mousavinezhad, and Dr. Gene Stuffle. I am very thankful for valuable input and inspiration they shared with me throughout 3 years of my studies. I am also grateful for all their help and support in non-academia field. It was a pleasure to meet and work along with such great researchers and brilliant minds – I will never forget that experience.

I would also like to extend my personal thanks to Polish community from Pocatello: Monika and Dawid Zydek, Eliza and Lukasz Borzadek, and Agnieszka and Piotr Lotowki. Living thousands of miles away from home is never easy however thanks to all aforementioned persons, holidays that we spent together, and time we shared I felt in Idaho like at home. Thank you for being there all the time.

Finally I would like to thank Dr. Leszek Koszalka and Dr. Iwona Pozniak-Koszalka - my advisors at the Wroclaw University of Technology. Their phone call on February 12, 2012 in which they asked "did I ever think about doing Ph.D. in United States of America" was so alike scenario of Hollywood movie in which a dreams come truth within a minute. I would never be able to full express how thankful I am for turning my life in that direction. I am so glad and proud that Polish students have a privilege to meet such wonderful persons like you.

# Table of Contents

| List of Figures                | ix                                        |  |

|--------------------------------|-------------------------------------------|--|

| List of Tables                 |                                           |  |

| List of Abbreviations          |                                           |  |

| Abstract                       | xiv                                       |  |

| Preface                        |                                           |  |

| Research theses                |                                           |  |

| Dissertation Overview          |                                           |  |

| Chapter 1. Literature review   |                                           |  |

| Chapter 1.1.                   | Multiphysics Simulation                   |  |

| Chapter 1.2.                   | General Purpose Graphic Processing Unit   |  |

| Chapter 2. Examined approaches |                                           |  |

| Chapter 2.1.                   | Pure GPU approach                         |  |

| Chapter 2.2.                   | Hybrid GPU/CPU approach                   |  |

| Chapter 2.3.                   | CUDA 6.5 enhanced hybrid GPU/CPU approach |  |

| Chapter 2.4.                   | Limitations                               |  |

| Chapter 3. Algorithms          |                                           |  |

| Chapter 3.1.                   | Proposed algorithms                       |  |

| Chapter 3.2.                   | cuBLAS operator                           |  |

| Chapter 4. Exp                 | eriments                                  |  |

| Chapter 4.1.                   | Hardware configuration                    |  |

| Chapter 4.2.                   | Plan of experiment                        |  |

| Chapter 5. Results             |                                           |  |

| Chapter 5.1.                   | Performance of Linear Algebra Operators   |  |

| Chapter 5.2.    | Performance of Multiphysics simulation |     |

|-----------------|----------------------------------------|-----|

| Chapter 6. Disc | cussion                                |     |

| Conclusion      |                                        | 102 |

| References      |                                        | 108 |

| Appendix 1      |                                        | 113 |

# List of Figures

| Figure 1. Generic multiphysics simulation system                                     | 13  |

|--------------------------------------------------------------------------------------|-----|

| Figure 2. Architecture of commercial simulators (ANSYS Multiphysics on the left,     |     |

| COMSOL Multiphysics on the right)                                                    | 15  |

| Figure 3. MOOSE Multiphysics architecture                                            | 17  |

| Figure 4. CUDA thread logical structure [54]                                         | 24  |

| Figure 5. GPU architecture [54]                                                      | 26  |

| Figure 6. Standard CUDA program flow                                                 | 37  |

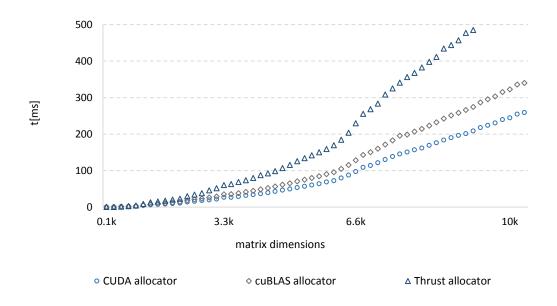

| Figure 7. Allocation method execution time                                           | 64  |

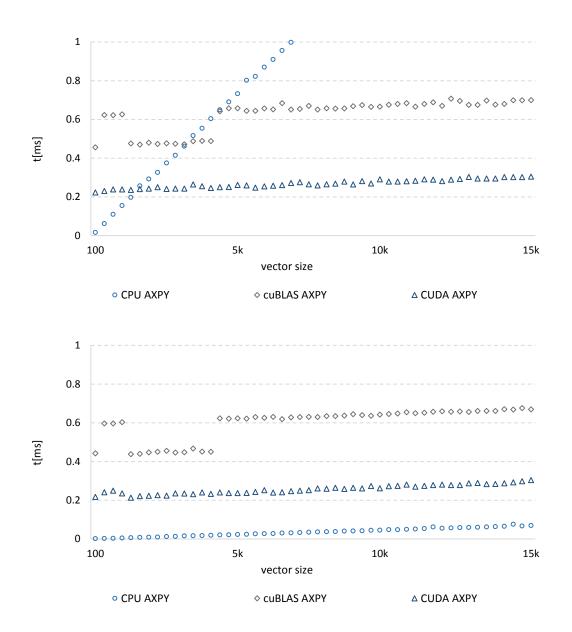

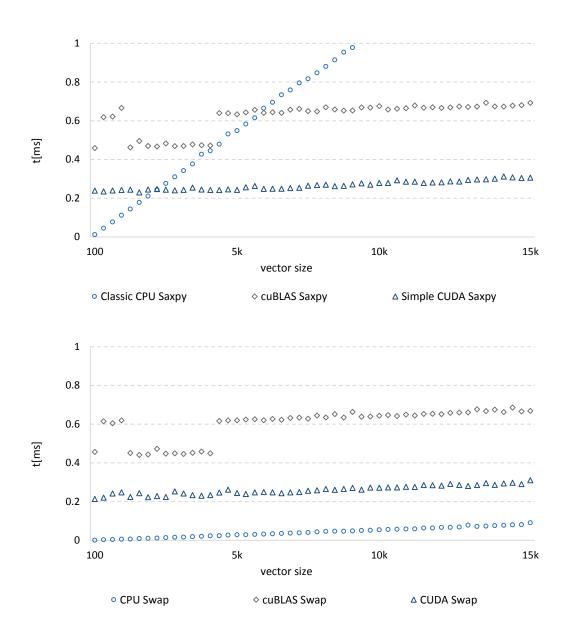

| Figure 8. AXPY operator performance (Thrust containers on the top, array containers  | on  |

| the bottom)                                                                          | 65  |

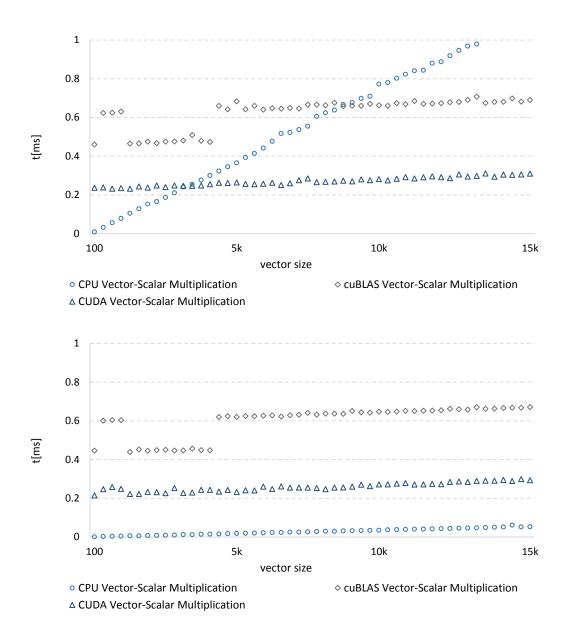

| Figure 9. Vector Swap operator performance (Thrust containers on the top, array      |     |

| containers on the bottom)                                                            | 68  |

| Figure 10. Vector-Scalar Multiplication operator performance (Thrust containers on t | he  |

| top, array containers on the bottom)                                                 | 70  |

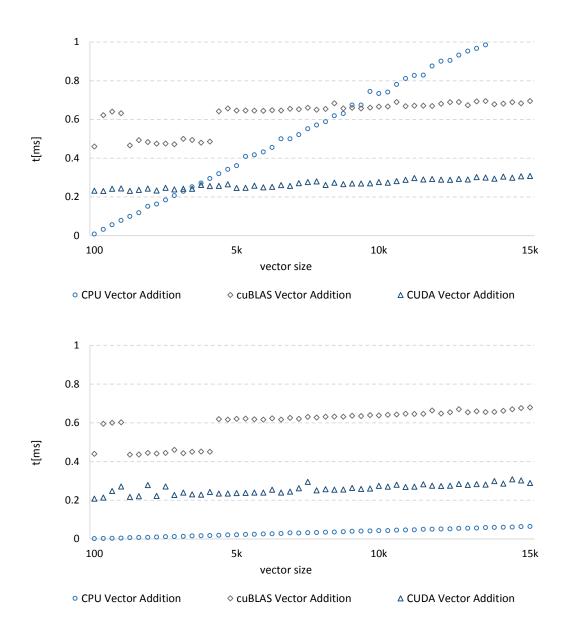

| Figure 11. Vector Addition operator performance (Thrust containers on the top, array | ·   |

| containers on the bottom)                                                            | 73  |

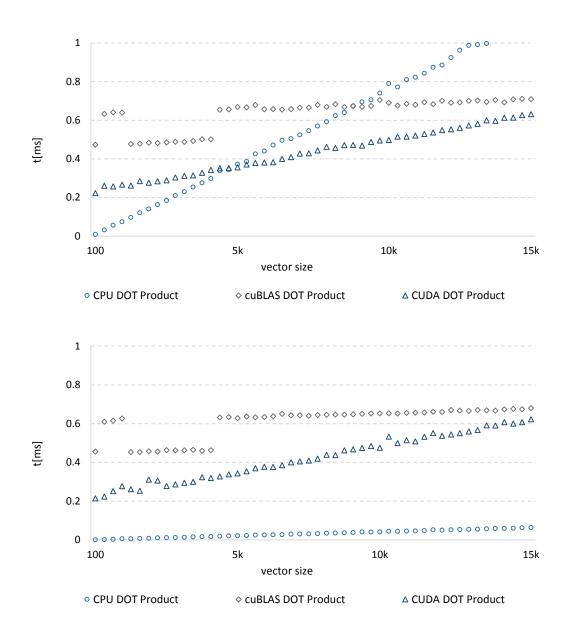

| Figure 12. DOT Product operator performance (Thrust containers on the top, array     |     |

| containers on the bottom)                                                            | 75  |

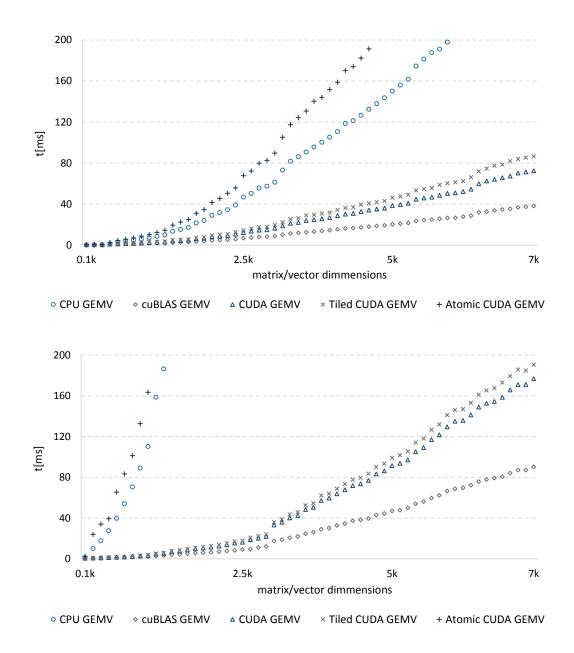

| Figure 13. GEMV operator performance (Thrust containers on the top, array container  | ers |

| on the bottom)                                                                       | 78  |

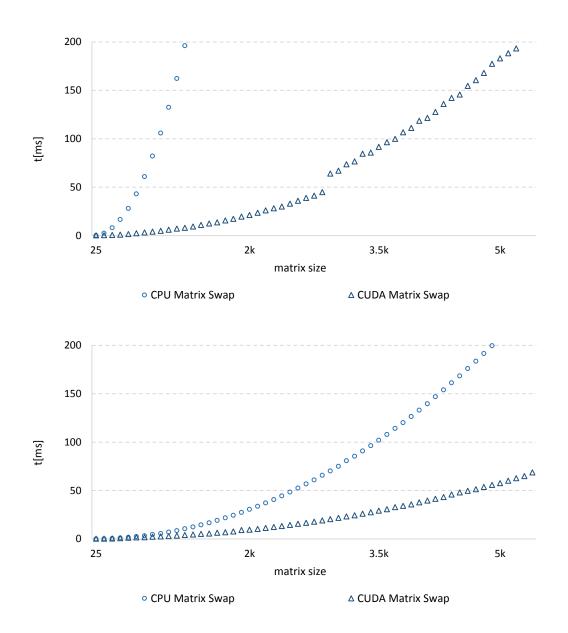

| Figure 14. Matrix Swap operator performance (Thrust containers on the top, array     |     |

| containers on the bottom)                                                            | 81  |

|                                                                                      |     |

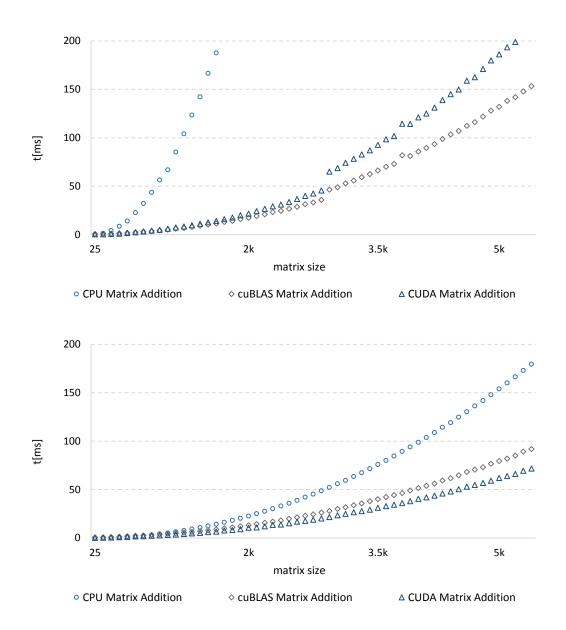

| Figure 15. Matrix Addition operator performance (Thrust containers on the top, array         |   |

|----------------------------------------------------------------------------------------------|---|

| containers on the bottom)                                                                    | 3 |

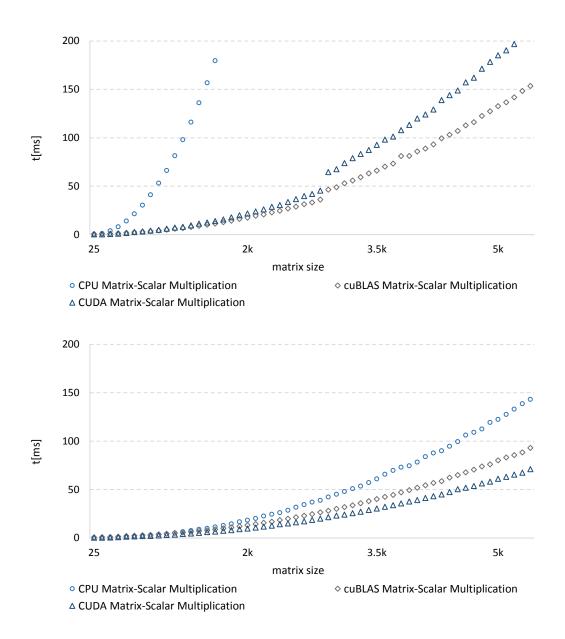

| Figure 16. Matrix-Scalar Multiplication operator performance (Thrust containers on the       |   |

| top, array containers on the bottom)                                                         | 5 |

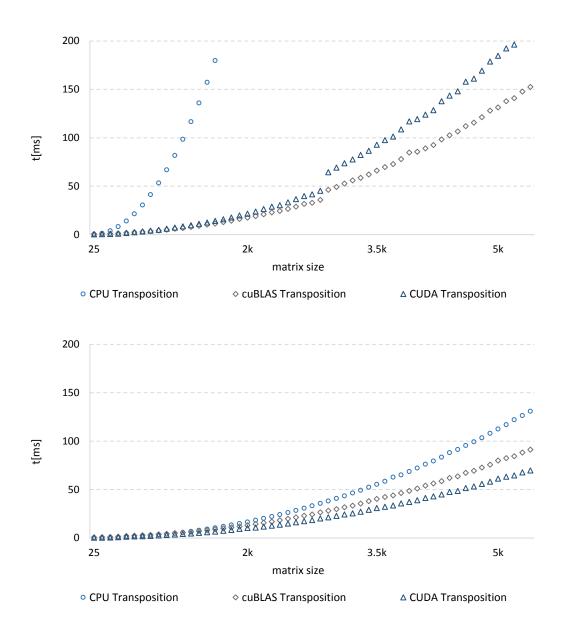

| Figure 17. Matrix Transposition operator performance (Thrust containers on the top,          |   |

| array containers on the bottom)                                                              | 7 |

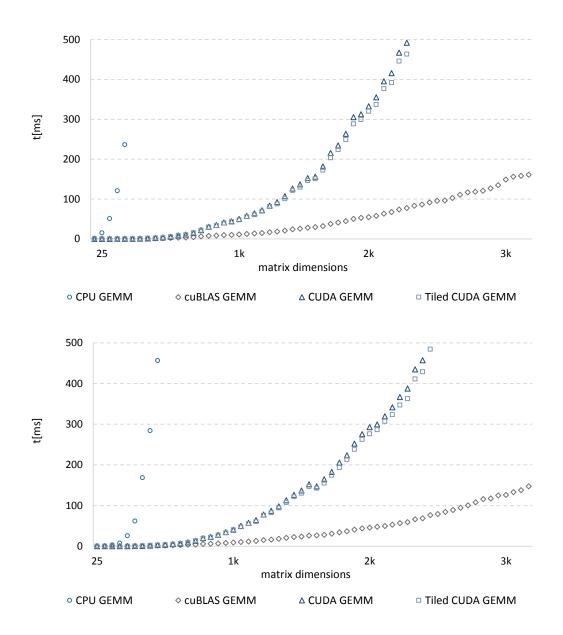

| Figure 18. GEMM operator performance ( <i>Thrust</i> containers on the top, array containers |   |

| on the bottom)                                                                               | 9 |

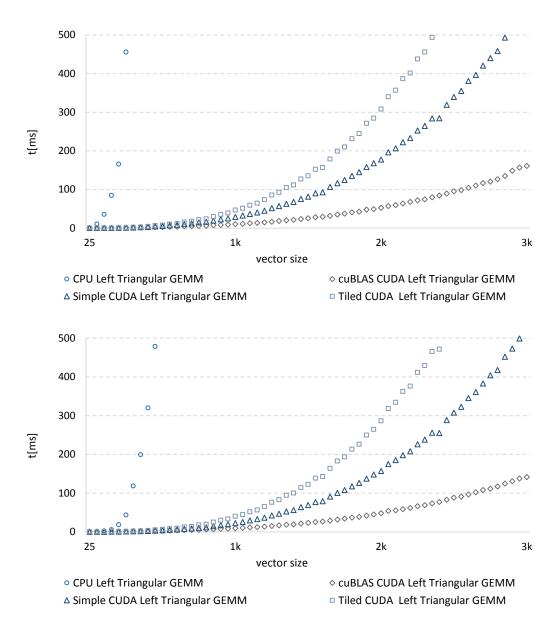

| Figure 19. Triangular GEMM operator performance ( <i>Thrust</i> containers on the top, array |   |

| containers on the bottom)                                                                    | 2 |

# List of Tables

| Table 1. cuBLAS methods and corresponding operators            | 51 |

|----------------------------------------------------------------|----|

| Table 2. NVidia Tesla K40 and NVidia Quadro 5000 specification | 55 |

| Table 3. Hybrid simulators performance                         | 96 |

## List of Abbreviations

- AMR Adaptive Mesh Refinement

- **BLAS** Basic Linear Algebra Subprograms

- **BLT** Bioluminescence Tomography

- CAD Computer-Aided Design

- **CUDA** Compute Unified Device Architecture

- **CPU** Central Processing Unit

- **DCC** Digital Content Creation

- **FE** Finite Element

- **flops** floating point operations per second

- **GPGPU** General Purpose Graphical Processing Unit

- **GPU** Graphical Processing Unit

- **GUI** Graphical User Interface

- **HID** Human Interface Device

- **HPC** High Performance Computing

- MOOSE Multiphyscis Object Oriented Simulation Environment

- MPI Message Passing Interface

- **PDE** Patrial Differential Equation

- **PETSc** Portable, Extensible Toolkit for Scientific Computations

- **SIMT** Single Instruction Multiple Threads

- **SM** Streaming Multiprocessor

- **STL** Standard Template Library

### Abstract

Multiphysics simulations, which involves a mathematical model of various physics phenomena expressed using partial differential equations, are integral part of projects and research conducted in number fields of science. It allows to gather knowledge about model, predict future condition, and saves a lot of time and money.

One of the most popular method of performing multiphysics simulation is a Finite Element method. As a numerical method it can be run by computers. Unfortunately large scale simulations require humongous amounts of computational resources. Yet, even then simulation process may take many days or even weeks.

General Purpose Graphic Processing Unit (GPGPU) is a new approach in high-performance computing that favorites highly parallel execution using hundreds of thousands of low-performance GPU cores over classic thousands of highperformance CPU executors. As the related work shows this approach can be very beneficial when applied to certain category of problems.

xiv

The goal of the research was to enhance the performance of existing multiphysics simulator by applying GPGPU model to it. It was important to preserve the functionality of existing simulator and to keep the interfaces unchanged so that applications built on it would not have to be modified.

To accomplish that goal three approaches were tested. In first of them it was assumed that whole library will be redesigned and reimplemented to be executed entirely by GPU. The approach led to failure because of highly object oriented design of existing simulator, extensive usage of Standard Template Library (STL) containers, and numerous branching instructions; all of these are poorly supported by GPGPU. In the second approach hybrid GPU/CPU implementation was proposed. All highly-parallel algebraic operators used by simulator were reimplemented to run on GPU; as a result custom GPU BLAS library was created. Results show that GPU/CPU approach was 10% faster than classic CPU approach. In third approach custom BLAS library and STL containers were replaced by *cuBLAS* library and *Thrust* containers, included in new release of CUDA programming model, respectively. Results show further improvement in terms of performance.

The research proves that reimplementing the existing multiphysics simulator to run on GPU is possible and results in enhancing the performance of simulation. Both the research and implementation are good starting point to evaluate the cost effectiveness, energy efficiency, and fault tolerance of proposed approach.

XV

### Preface

"Mathematics is the language of nature" – this sentence was frequently said by mathematics prodigy, gifted scientist and a brilliant mind – Maximilian Cohen – the main protagonist of movie Pi from 1998 [1]. Quoted phrase is an entry point to his research, which goal is to discover a universal pattern that describes the universe. Although the concept of a comprehensive pattern or equation can be classified as math fiction, assumption that "mathematics is the language of nature" might be quite probable thesis. To support it one can refer to number of various papers and essays written throughout the centuries and especially to texts from XX century. Galileo Galilei, an Italian physicist from XVI century, wrote [2] that "philosophy [nature] ... is written in mathematical language." Few hundred years later Sir James Jeans, British physicist, suggested in [3] that "God is a Mathematician." The most famous and influential essay, however, was written in 1960 by Eugene Wigner - Noble Prize awarded physicist and mathematician. In the paper commonly known as Unreasonable Effectiveness [4] author expressed the special role of mathematics in modern fields of study and, what is the most important, pointed out how mathematical concepts developed for certain case, are often applicable to problems that are far from original context.

As an example author referred to Newton's law of universal gravitation which origins in observation of free falling object on the surface of the Earth. The same law can be easily adapted to describe forces generated between the planets. Later in the text Eugene Wigner brought up Maxwell's equations that originally meant to model the magnetic and electric phenomena. Almost 30 years later the same equations were used by David Hughes to describe his new discovery [5] radio waves.

Traces of mathematics can be found everywhere. High school students apply simple physic formulas, and therefore mathematics, calculate distance, velocity, and acceleration. Undergraduate Sociology students data frequently refer to Gaussian distribution since surprisingly often statistical data generated from surveys perfectly match the curve of Gaussian function. Gaussian distribution as a tool was invented decades before the modern social science [6]. Moreover the function contains number  $\pi$  which origins are in Ancient Egypt and was used in completely different context [7]. Analogous situation can be observed in Structural Engineering. Concepts like bending moments, compressions, or slope and deflections were for centuries intuitively understated by firsts masons or builders. When physical background of these concepts were finally discovered by Leonardo da Vinci in late XV century and developed by his successors, like Leonhard Euler [8], in XVIII century it appeared that mathematical background already exists. Following that path even further one can observe similar tendency in quantum mechanics and string theory. First of them uses complex numbers which in 1545 century were just a trick to find real roots of certain polynomial equations [9], second is based on created in 1813 non-Euclidean geometry which was treated like a joke until 1914 – the beginning of string theory era.

All of these examples allow to presume that mathematics impersonates reversed visionary. In thesis author's personal opinion visionaries, rather that foreseeing future, are setting a flag that is later pursued by scientists and engineers around the world. If so then mathematics may be compared to ready solution that is waiting for a visionary to foresee an application for it. This scenario is also applicable to partial differential equations and multiphysics simulation.

### **Research theses**

Throughout last two decades an attention of researchers from various fields of science is turned at mathematical models and multiphysics simulation. Modern computer simulation and Computer Aided Design allows engineers from different fields to increase the effectiveness of their work and research. This trend is not surprising since multiphysics simulation is crucial for almost every civil engineer project, automobile design facility, chemical laboratory, and nuclear power plant.

Simulation helps to improve the understanding of functionality and behavior of a model. Using models allows prediction of future conditions and foreseeing possible issues. Very often simulating a model is the only potion of a problem that can be solved. Furthermore, multiphysics simulation, saves a lot of time, energy, and subsequently, money.

Unfortunately when one is willing to apply multiphysics simulation to very complex model then he may quickly hit the performance barrier. In fact increasing complexity of model causes rapid growth in computational resources consumption. As a result complex simulations are a domain of research facilities equipped with extremely expensive supercomputers. Although manufactures release more and more advanced supercomputers the "appetite" for computational power of scientists is unsatisfied. The answer for this problem may be seek in modern technologies that break up with old approaches to computations. Such an approach is General Purpose Graphical Processing Unit approach.

The idea of GPGPU assumes using modern Graphical Processing Units to perform general purpose computing. GPU is composed of a number of independent multiprocessor units called Streaming Multiprocessors. SMs execute in parallel thousands of instances of code called kernels. Although a single processor within a SM does not provide high performance and the single thread is not executed as fast as it would be on a modern Central Processing Unit, the ability to execute a massive number of threads in parallel gives GPU exceptional performance. This observation and assumption lead to the hypothesis that:

# Applying GPGPU to multiphysics simulation may results in shortening simulation time while keeping the same results.

Hypothesis stated in that way is generic and there are many ways to confirm it or to prove it wrong. To start witch one can choose from different GPU manufacturers which may and will have an impact on performance, power consumption, and accurateness. Moreover brand of device can dictate the programming model – GPUs produced by *AMD* can execute code written in *OpenCL* whereas *NVidia* GPUs can, as for today, execute both. To continue, underlying hardware enforces developers to focus on different architecture-specific aspects crucial to use computational resources of GPU in full. Secondly one may want to work on a specialized simulator that can be applied to a small domain – e.g. heat

transfer – or develop framework that can be applied to wider spectrum of simulations. Finally GPGPU approach may be a starting point to implement new multiphysics simulator or applied to existing software. In first scenario program can be tailored to underlying architecture and therefore very effective; in second scenario framework design may compromise the performance however all application already build on the framework will remain functional. To narrow the scope of research three questions were asked:

- Is it possible to re-implement existing multiphysics simulation framework without affecting existing software build on the framework?

- Will the GPGPU approach results in better performance of multiphysics simulation framework?

- Would the potential performance gain be worth of time and money required to re-implement and test thoroughly the framework and provide required hardware?

These research questions point the direction in which research will be leaded and endorse the goal of the research.

> Enhance the performance of existing multiphysics simulator by applying General Purpose Graphical Processing Unit model to it.

Scope of the research specified in that way makes it accomplishable in reasonable period of time and, in the same time, does not affect the generality of consideration.

### **Dissertation Overview**

#### a. Content of the Dissertation

Following dissertation is divided into six main chapters. The order of chapters and sub-chapters reflect the order in which the study and the research were conducted. This manuscript covers both successful ideas but also concepts that failed. The dissertation consist of:

*Chapter 1: Literature review* – this section is divided into two sub-chapters. First one covers the topic of multiphysics simulation with emphasis put on Finite Element method concept and implementations. Second part is focused on GPGPU technology related to CUDA and CUDA-enabled hardware. Each sub-chapter consist of introduction to basic concepts and literature review of the corresponding topic. Literature review part presents other research in which concepts touched in this thesis were considered, describes benefits and limitations of these approaches, and exhibit related work which is goal similar to the one set in this research.

*Chapter 2: Examined approaches* – in this section all examined approaches to speedup simulation time were explained. In first sub-chapter holistic approach is presented. In

this approach it was assumed that the complete process, that single CPU thread executes, can be translated to CUDA and launched by a single GPU thread. The design problems, architecture limitations, and major obstacles to accomplish the goal in this way were presented. Second sub-chapter is focused on hybrid CPU/GPU approach in which heavy computational parts of code were ported to CUDA and tailored into multiphysics framework as a layer between framework and hardware. The concept, advantages, and drawbacks of the approach were discussed. In last part of the chapter hybrid approach modified to use in-build libraries from the newest CUDA release was presented. New CUDA programming model includes number of libraries which may be very beneficial, in terms of performance and code robustness, to implement especially that it would not affect the idea of hybrid approach. It is enough to modify mentioned earlier layer between multiphysics framework and hardware. Therefore no further modifications in multiphysics framework itself would be required.

*Chapter 3: Algorithms* – in this chapter all methods designed and implemented were presented. Each method, and approaches to implement it, is considered in separate sub-chapter in which appropriate description, implementation details, and CUDA code is presented. Performance of parallel GPU application relies heavily on used technique and problem it is applied to – mechanisms that work great for certain problems may have terrible performance for others. Therefore every method was implemented in more than one way in order to examine different concepts and techniques. Different implementations are considered in sub-chapter specific to the method they implement.

*Chapter 4: Experiment environment* – this chapter describes the environment in which experiment were carried out. The detailed hardware configuration of machines used in the research was presented; the differences between them was described and detailed explanation on key differences was provided. In this section crucial concerns that follows every performance tests were discussed. Among others special attention was paid to external nondeterministic factors that may have negative influence in results. Because of that steps to reduce the noise and techniques to filter out remaining noise were proposed. The general plan of experiment was expressed using simple mathematical formulas. The details of test cases – like size of matrices that are about to be multiplied – are provided together with results in next chapter.

*Chapter 5: Results* – in this section obtained results were presented and briefly discussed. Performance evaluation was grouped in four sections. In first two of them hybrid CPU/GPU approach was considered. Firstly effectiveness of CUDA-enabled algorithms were evaluated and referred to performance of corresponding CPU algorithms; second the algorithms were introduced to simulation framework and performance of whole system was inspected. In second two subsections analogous scenario was used. First CUDA-enabled algorithms were implemented using features of new CUDA programming model are implemented into simulation software. Their efficiency was referred to previous results. Second multiphysics simulator was modified and compared to previous version of the application. Also in this chapter accurateness of GPU algorithm was assessed and compared to accurateness of CPU algorithm.

*Chapter 6: Discussion* – in this chapter results obtained from the experiments are discussed. Performance of GPU-enabled algorithms were assessed by comparing efficiency of different versions of the same method to each other and to effectiveness of classic CPU method. Later on the performance of proposed algorithms were compared to performance corresponding algorithms from commercial library supplied with new version of CUDA framework. Furthermore the behavior of every algorithm is discussed together explaining the reasons of why some algorithms are better than others. In this section it is also discussed how selection of CUDA algorithms may affect overall multiphysics simulation performance. It is also described why in certain cases hybrid GPU/CPU approach results in performance loss and what requirements have to be fulfilled in order to enhance the performance.

*Conclusion* – in last section of this dissertation a brief summary of conducted work was presented. In this section advantages and disadvantages of proposed approach are presented and the answers for research questions are formulated. In this part guidelines regarding future work are presented, aspects that were omitted in this manuscript but are worth or even must be considered are pointed out, and limitations are discussed. Also the thesis of the dissertation is reevaluated in terms of initial expectations, observations, results, and limit of proposed approach.

#### b. Self - Citations

The following papers played important role and contributed to research presented in this dissertation and contributed:

- Solving PDEs in Modern Multiphysics Simulation Software [10]: presents the concept of multiphysics simulation in HPC. It focuses on the architecture of multuphysics simulators and underlying libraries. In this paper code analysis of *libMesh* was conducted.

- *Matrix Multiplication in Multiphysics Systems Using CUDA* [11]: first implementation of CUDA algorithm that later was composed, together with other methods, custom GPU BLAS library were presented and evaluated in terms of efficiency.

- *Hybrid GPU/CPU Approach to Multiphysics Simulation* [12]: first iteration of GPU-enabled libMesh library is proposed. Instead of one-to-one translation from CPU thread to GPU thread hybrid approach is proposed.

- Effectiveness evaluation of cuBLAS and Thrust CUDA 6.5 libraries [13]: alternative implementation of previously proposed GPU-enabled BLAS operator was presented in this paper. It was an entry point for proposing second iteration of *libMesh* library implementation that uses *cuBLAS* operators and *Thrust* data structures

- Problem-Independent Approach to Multiprocessor Dependent Task Scheduling [14]: points out importance of parallel processing and importance of proper job management in HPC environment

### Chapter 1 Literature review

### Chapter 1.1. Multiphysics Simulation

Multiphysics simulation is a complex process that requires significant time and computational resources. It involves a number of physical phenomena usually described by PDEs – the process of multiphysics simulation is therefore equivalent of solving system of PDEs. Currently one of the most popular approaches to solve PDEs is the FE method. The method was originally developed in 1943 by A. Hrennikoff and R. Courant, it gained popularity in 1960 when applied to the problem of electromagnetic wave propagation [15]. Simulations are widely applied in most major fields of science and business like nuclear power plants, civil engineering, and automotive. Very soon after FE-based simulation become popular market responded with wider variety of multiphysics simulation software like *COMSOL Multiphysics* or *ANSYS Multiphysics*, but also open source software like the, *MOOSE Framework*.

Engineers and scientists are eager to use new technologies that may offer promising possibilities for performing simulations faster and easier. Although these aforementioned applications can be easily used on a typical modern personal computer, more advanced

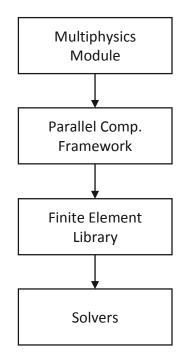

Figure 1. Generic multiphysics simulation system

simulations that incorporate a significant number of physics phenomena requires very precise results. These simulations are performed on meshes assembled from millions of shapes and require an enormous amount of computational resources. Resources are, as usual, limited and because of that researchers search for simulation framework that suits or can be accustomed to suit their needs.

### a. Generic approach to multiphysics simulation

The general simulation approach used in most of FE-based simulators can be presented by diagram in Figure 1 [10]. The process starts with defining mathematical model of multiphysics phenomena problem with corresponding properties and expressing it in manner required in underlying framework. This step is performed in first layer of

generic simulator diagram called Multiphysics Model. Top level layer provides user a set of helper functions, methods to import data from CAD applications, or very often a graphical interface in which user can assemble model and set appropriate properties. Input data is the passed to Parallel Computational Framework. By definition each framework is a set of more or less compound wrapper functions that group calls of generic methods from underlying libraries in order to provide easy access to problem specific system. In this scenario second layer of simulation system is responsible for preprocessing of input data and parameters; base on that appropriate simulation plan, data structures, monitoring procedures, and thread pool are created. Finally the simulation is started and, from this point, is performed by FE library and FE solver [10]. Another role of Parallel Computational Framework is maintaining the contact with user and informing about status of the simulation. A popular approach to handle communication is through console log. The next layer, FE library, handles the simulation. This layer supplied the framework with utilities to perform FE based computations like input/output mechanics for meshes, error handling protocols, and interfaces to solver packages. It is also responsible for managing parallel processing across multiple computational nodes. Last layer is a Solver layer which consists of set methods that solves systems of differential equations, BLAS operators, and basic data structures with associated primitives [16]. The layer is responsible for solving an actual set of PDE provided by FE library in efficient way; because of its proximity to hardware it often provides implementation MPI and profiling tools. Results generated by Solvers are passed back to FE library which proceeds to next step of simulation or prepares the output and transmit it to higher layers.

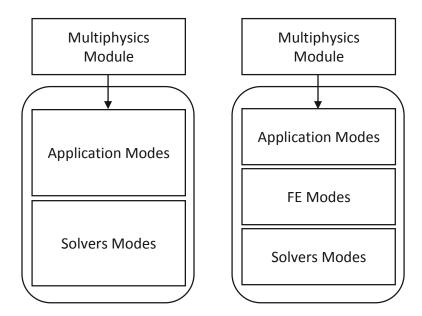

**Figure 2.** Architecture of commercial simulators (ANSYS Multiphysics on the left, COMSOL Multiphysics on the right)

### b. Commercial multiphysics simulators

Currently there are two leading commercial multiphysics simulation systems: *COMSOL Multiphysics* and *ANSYS Multiphysics*. Both are an interactive environment for modeling and solving various scientific problems based on PDEs using FE method. Applications offer a user friendly interface – multiphysics module – that speeds up defining of problem and simulation parameters. Both applications provide number of API and plugins that allow to integrate simulator with custom applications written in most major programming languages including *MATLAB* or to import data from CAD applications. *COMSOL* and *ANSYS* are widely used in areas like acoustics, heat transfer, photonics, and structural mechanics [17] [18]. Moreover, as the documentation points out, their architecture – Figure 2 – has very close resemblance to generic model presented in Figure 1. Both simulators provides satisfying performance and wide spectrum of appliances, however there are cases when more flexible, problem specific, and scalable solution is required – this is when custom frameworks like *MOOSE* becomes handy.

#### c. MOOSE Multiphysics

MOOSE is created and developed at INL. It is the multiphysics parallel computational framework used for solving computational engineering problems. Application was designed to reduce time and expense, required to develop new software, and to perform simulation in organized, manageable, and coordinated manner. MOOSE can be used, similar to its commercial competitors, in areas like heat conduction, fluid flow, solid mechanics, thermo-mechanics, and many others [19]. Originally a government application, it went open source on March 21<sup>st</sup>, 2014 [20]. Since then popularity of packages MOOSE is built on and MOOSE itself is growing in academia.

MOOSE allows performing up to 3D analysis. System is capable of using unstructured mesh that is built from shapes such as triangular, quadrilateral, tetrahedral, prism, and others. Framework also provides developers huge variety of post processing options [19]. All MOOSE functions can be performed in parallel in CPU cluster, e.g. at INL system the framework is used on supercomputer that number of cores is counted in thousands. Currently MOOSE supports Jacobian-free Newton–Krylov method with Physics-Based Preconditioning for solving tightly coupled multiphysics modules [21].

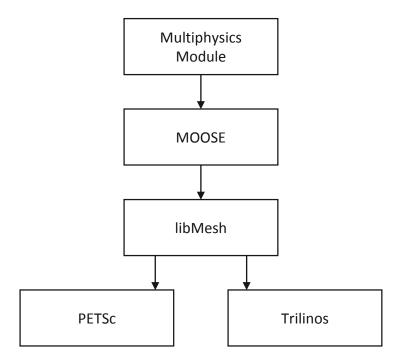

Figure 3. MOOSE Multiphysics architecture

MOOSE is an object oriented FE-based framework. This means that framework does not enforce use of integrated FE libraries or solvers (system can use any FE library available and best solvers peculiar to the selected library). In MOOSE, interfaces to one FE library (*libMesh*) and two solvers (*PETSc* and *Trilinos*) are provided; however, the framework is capable to use any other FE-based software. The structure to solve multiphysics problems using *MOOSE* is shown in Figure 3 [10].

As it can be seen MOOSE architecture matches generic ideally. Multiphysics Model layer of MOOSE framework is an application written by user based on methods provided by MOOSE. In this layer input data like mesh of an object and list of properties has to be specified. MOOSE layer is an interface between user code and FE library; it initializes all underlying data structures, preprocess and validates input, and starts the simulation. *LibMesh*, as the method of weighted residuals, processes the FE computations after receiving the weak form of PDEs from *MOOSE*. Solver, as a tool finding PDEs' solutions, can be subset of FE Library for providing large scale parallel computing resources [10].

LibMesh is frequently used, especially after *MOOSE* went open source, in academia and commercial researches from vast variety of field of science. In [22] author simulated random initiation and subsequent propagation of interacting thermal cracks in a ceramic nuclear fuel pellet using coupled mechanics, heat conduction, and fracturing. The simulation allowed to precisely demonstrate the formation of cracks during the initial power rise and power ramp downs. A problem of estimating a hydrogen behavior and distribution in nuclear fuel rod was considered in [23]. *LibMesh*, as a part of *MOOSE* framework, was applied to model composed of diffusion under concentration gradient and temperature gradient. The simulations predicted that hydrogen tends to accumulate on colder areas right before it precipitates and as a result degrade the cladding ductility.

### d. libMesh

The *libMesh* is a framework that uses arbitrary unconstructed discretization for numerical simulations of partial PDEs. First version of application was developed at the University of Texas at Austin in 2002. However, a major contribution in developing *libMesh* throughout ages came from INL, MIT, and PECOS Center [24].

The *libMesh* library was designed and implemented to simply parallel, adaptive, and multiscale multiphysics FE simulations. Designers wanted to achieve that by centralizing physics independent technology to support parallel and adaptive unstructured mesh-based

simulations. This approach allows users to focus on the specifics of a given application without considering the complexities of parallel and adaptive computing. Thanks to that *libMesh* proved a robust environment for a wide range of physical applications [10].

The library uses AMR in FE simulations. AMR can produce efficient meshes for refining solution through the coarsely resolved base-level regular Cartesian grid [25]. Framework supports 1D, 2D, and 3D simulations on big variety of geometric and FE types. The library provides interfaces to libraries that perform linear algebra computations, meshing, and partitioning.

Although the simulation is already performed in parallel with MPI on multiprocessor supercomputers, large scale simulations of models represented by a multimillion cell mesh still calls for more computational power. Since the frequency boundary of the CPU was almost reached, the only solution is to increase the number of computational nodes. However, upgrading existing supercomputers by adding new CPUs is very pricey and the increase of performance may be relatively small compared to the cost of modernization. IT seems that using GPGPU might be beneficial in this case however according to documentation no GPU support is provided and is not planned to be provide in the nearest future [24] [12].

#### e. PETSc

*PETSc* is a suite of data structures and methods designed for the scientific applications modeled by PDE. Library supplies developers with building blocks for the implementation of large-scale application executed, in parallel as well as in series, by

computers [26]. *PETSc* includes a suite of parallel linear, nonlinear equation solvers and time integrators. Components may be used in custom applications written in most major programming languages like FORTRAN, C/C++, Python, or MATLAB<sup>1</sup>. Through implemented MPI standard for all message-passing communication, *PETSc* provides many of the mechanisms needed within parallel application [27]. The library is organized hierarchically and by that enables users to employ the level of abstraction that is most appropriate for a particular problem [10].

*PETSc* consists of a variety of libraries. Each library implements certain family of objects and methods related to that object. Object form a hierarchy that enforces user to follow specified order of execution and to use only classes required by the simulation. Modules provided by *PETSc* are as follows: index sets for indexing into vectors, renumbering, etc.; vectors and matrices as a basic data storage with basic operators and subroutines; managing interactions between mesh data structures and vectors and matrices; over fifteen Krylov subspace methods; number of preconditioners, including multigrid, block solvers, and sparse direct solvers; nonlinear solvers; time steppers for solving time-dependent nonlinear PDEs including support for differential algebraic equations [28].

### f. Trilinos

The developer of *Trilinos* – Sandia – historically did a work in area of developing scalable solver algorithms and software. Their software, however, was often enclosed within single context of a specific application code, providing a good robust solver that

<sup>&</sup>lt;sup>1</sup> MATLAB supports only sequential execution of *PETSc*

specifically meets the needs of that application. The best example is *Aztec*, solver developed for *MPSalsa* project and only later extracted for use with other applications. Despite robustness of the solutions, applications were rarely reused in different projects and for different purposes. Therefore at some point developers decided to create a library of various project that would have a wide spectrum of appliances in different areas of scientific experiments – that decision set the cornerstone for *Trilinos* project [29].

*Trilinos* is the library of packages for solving the large-scale and complex multiphysics problems [30]. Application supports number of linear, nonlinear, and eigenvalue problems. *Trilinos* differs from *PETSc*, which has independent packages. In fact, Trillions could easily use *PETSc* to provide a variety of capabilities through the documented abstract interfaces without modifying their source code [31]. In addition, *Trilinos* supports also external solvers, like *PETSc*, by supplying users with interfaces. Therefore application can be used also as a framework placed between FE library and solver. Each *Trilinos* ' package is the independent unit implemented using a particular algorithm [10].

*Trilinos* provides packages like nonlinear solvers like *NOX*, *LOCA*, and *GlobiPack*; linear solvers e.g. *AztecOO*, *Belos*, and *Komplex*; eigensolver Anasazi; preconditioners like Meros, *ML*, *Ifpack*; Basic Linear Algebra module *Epetra* and *Jpetra* implemented in C++ and Java respectively; common services package *Teuchos*.

#### g. Conclusion

As the documentation points out both *Trilinos* and *PETSc* support MPI, shared memory pthreads, and GPUs through CUDA or OpenCL. *PETSc* supports also MPI-GPU parallelism. Therefore FE solvers layer is rather unlikely to be an obstacle to overcome when porting the simulator to GPU. Because of that these packages will not be considered in this thesis, however their GPU capabilities will be used in experiment that assess the effectiveness of redesigned multiphysics simulator.

## Chapter 1.2. General Purpose Graphic Processing Unit

Throughout last couple years the area of HPC experienced a rapid and effective changes in field of both software and hardware. According to TOP 500 ranking the most powerful machine, ranked in June 2013 [32], has twice as much computational power as previous, ranked in November 2012, leader. Such a humongous progress in terms of computational resources originates from current trend to relay on highly parallel processing rather that relatively small cluster of high-frequency CPUs. In 2012 a version 3 of MPI standard [33], used by nearly every supercomputer, was approved. A year later, in June 2013, new version of another notable API - *OpenMP* - was released [34]. *OpenMP* focuses strongly on shared memory multicore processing and fill the niche left by MPI. A milestone in HPC, however, was introducing General Purpose Graphical Processing Unit. Concept assumes that parallel execution by thousands of low performance cores gives better result that executing the same program by just few high performance CPU. The cornerstone of idea is the limitations that hardware engineers approached. Moore's Law states that the

number of transistors located in a dense integrated circuit doubles every two years [35]. However increasing quantity of transistors placed on the same area eventually cause major growth of temperature. This lead to malfunctions or even irreversible damage. Therefore the answer to demand for computational power was to process in parallel.

In GPGPU SMs, that GPU consists of, are capable of executing enormous number of threads and therefore act as a cluster of low performance cores. The idea appeared to be so good that in 2010, soon after *NVidia* released parallel computing platform named CUDA, GPGPU revolutionized and dominated the market of HPC. As the TOP500 ranking shows in June 2010 only one supercomputer ranked in TOP 5 of the ranking was using GPU whereas in November 2010 three machines from TOP 5 (including the leader that doubled performance of his predecessor) relied on GPU [32]. Market responded almost immediately and main *NVidia* competitors on hardware market – AMD (that acquired ATI in 2006) and *Intel* - released their solutions – *AMD Radeon* GPU with *OpenCl* and Intel *Xeon Phi*. Both companies quickly caught up nevertheless NVidia still remains the leader due to new cutting-edge devices, extensive support, and new releases on CUDA framework.

#### a. CUDA programming model

From developer point of view kernel is a single, usually short, function that is executed by GPU threads. Thread is the most basic execution structure in GPU environment. Kernels are written in CUDA language which is a C++ with minimal

extensions; nonetheless it is important to remember that not all C++ features are supported by GPU kernels.

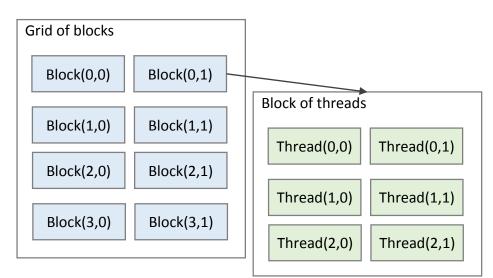

When kernel is called one has to explicitly specify how many threads are assigned to it; each thread assigned to kernel will execute exactly the same code. Threads are grouped in one-, two-, or three- dimension blocks. Each thread within a block of threads can be identified by properties *threadIdx.x*, *threadIdx.y*, and *threadIdx.z*; these properties are coordinates of thread. The property is always defined; when block is one-dimensional only then *threadIdx.y*, and *threadIdx.z* will be 0. Block *x*-, *y*-, *z*-dimension may be retrieved by calling *blockDim.x*, *blockDim.y*, and *blockDim.z* respectively. Logical

Figure 4. CUDA thread logical structure [54]

structure of thread mesh is presented in Figure 4. Maximal possible dimensions of block, as well as maximum number of threads within a block, are dictated by CUDA capability of used GPU [11].

Blocks of threads forms another structure called grid. Similar to block, grids may have up to three dimensions. Each block is identified by its coordinates: *blockIdx.x*, *blockIdx.y*, and *blockIdx.z*; maximal dimensions of block and maximal allowed number of threads within a block are related to CUDA capabilities of GPU. Threads within one block share one SM and one portion of memory. It allows to cooperate with each other to speed up execution of kernels.

As it was aforementioned each thread executes exactly the same part of code. Therefore the factor that distinguish the obtained result is where the thread is located. Base on block coordinates, block dimensions, and thread coordinates it is possible to calculate absolute coordinates of thread within an entire execution logic structure. Traditionally the absolute coordinates of thread are named idX, idY, and idZ can be calculated from equations (1), (2), and (3). The coordinates, distinct for different threads, differentiates the context under which thread runs.

$$idX = blockIdx. x \cdot blockDim. x + threadIdx. x \tag{1}$$

$$idY = blockIdx. y \cdot blockDim. y + threadIdx. y \tag{2}$$

$$idZ = blockIdx.z \cdot blockDim.z + threadIdx.z$$

(3)

To conclude the developer point of view, the general idea of parallel programming is to visualize the problem as a mesh of smaller sub problems and to overlay a logical structure of threads onto it so that threads are mapped to sub problems. The general rule that can be applied to most cases is that to divide the problem as much as possible and

**Figure 5.** GPU architecture [54]

employ as many threads as feasible in order to increase performance and level of parallelism.

#### b. GPU architecture

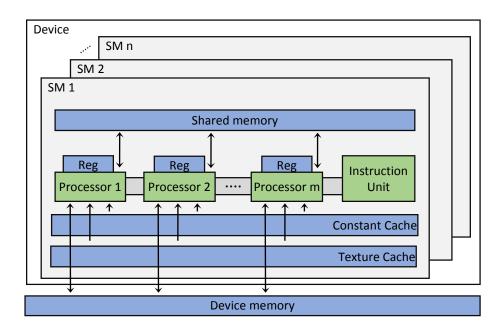

Figure 5 presents the hardware architecture of GPU. GPU consists of set of Streaming Multiprocessors and global memory; each SM is built on set of interconnected processors, instruction unit, and additional levels of memory.

Each block of threads is assigned to a single SM and is executed entirely within a context of that SM. Although one SM may host more than one block of threads, one block cannot be split among multiple SM. Each SM is equipped with scheduler. It is responsible for scheduling bathes of threads, called warps, to processors within the SM. Size of warp is number of threads that will be executed in parallel by SM. Currently size of warp is 32,

nonetheless it is very likely to be changed in oncoming generations of GPU [11]. Each thread is executed by a single processor, therefore size of warp is also number of processors, sometimes called CUDA cores, within one SM. It allows to calculate number of SM in GPU by simply dividing number of processors, provided by GPU datasheet, by warp size.

GPU executes threads in SIMT manner. It means that an instruction unit, shared by all processors within SM, issues one and the same instruction at a time to each processor.

In CUDA programming model, presented in Figure 5, three types of memory are distinguished. First of them is global device memory – the main memory of the device. Usually it is implemented using DDR5 RAM. It can be accessed by every thread from every block. Because of large number of threads that can access this storage at Global memory is slow and therefore it is not recommended to store frequently accesses data there [36].

Second memory type is shared memory. This memory resides in SM and some part of the memory is assigned to a single block executed by SM. This part of memory can be accessed only by threads from block to which memory was assigned. It is very fast and efficient so the most frequently used data, especially the one that is used by many threads in the same block, should be placed here [11]. Third type of memory is local memory that can be used only by a thread that is assigned to this memory.

c. CUDA 6.5

New CUDA framework brings up a number of improvements including resolved previous version issues, support for CUDA Fortran, profiling tool interface, and number of libraries including *Thrust* and *cuBLAS*. Both of these libraries were an open source project a long before CUDA 6.5 [37]. Thrust is a GPU enabled equivalent of famous STL. STL was first introduced in '90 and since then is a crucial part of many large projects. STL offers a set of flexible and optimized data structures together with corresponding optimized methods like sorting, searching, data sets merging etc. STL greatly improved the development process since programmers did not have to implement their own versions of common container-specific methods. Thrust library is based on the same idea like STL – even containers and methods kept the same names – and simplifies the process of CUDA code development. In addition Thrust allows to use GPU to store and manipulate data in parallel, and therefore more efficient, manner (e.g. sorting a list in parallel). CuBLAS library is GPU enabled BLAS which is a set of subroutines that performs common linear algebra operations in parallel. Origins of BLAS can be found in 1979 when it was a platform independent Fortran library that supplied developers with basic linear algebra operators that could be used as a blocks in bigger applications. CuBLAS offers a set of carefully designed and very well optimized linear algebra operators [38] which are encapsulated in easy to use wrapper function. Because of that cuBLAS not only simplifies the development process but also offers cutting-edge performance. Both Thrust and *cuBLAS*, being a response for developers (used to program in C++) needs, earned huge popularity eventually were approved by NVidia and include in CUDA 6.5 framework.

Possibilities and potential performance of *Thrust* and *cuBLAS* libraries are very promising therefore incorporating them in multiphysics simulation framework like

MOOSE may bring significant performance enhancement. Equally important is the simplicity and flexibility offered by mentioned libraries. Because of that eventual refactor of existing *MOOSE* implementation may be much easier that reimplementing it in plain CUDA. The goal of the paper is to evaluate the performance and usability of *Thrust* and *cuBLAS* libraries and, as a result, asserting their usefulness in multiphysics simulation software.

Although both *cuBLAS* and *Thrust* are relatively young part of CUDA framework the libraries itself exist for a few year and were able to attract significant attention of researchers and developers. In [39] authors evaluated the effectiveness of three level 3 *cuBLAS* methods – SGEMM, SSYRK, and STRSM – and proposed improved versions of these. In the experiment version 1.0 of *cuBLAS* was used; all kernels were executed by *NVidia GeForce* 8800. Authors started with evaluating the impact of size of input matrices on performance of *cuBLAS* operators and then moved to examining the relation between performance and matrix processing operator itself. As a result authors confirmed the effectiveness of algorithms and the improvements they proposed focus on combining *cuBLAS* methods with each other, dividing the work between GPU and CPU (which normally is idle when GPU executes the kernel), and resizing input matrices to maximize number of threads executed in one cycle.

Similar problem was also investigated in [40]. Authors made an effort to evaluate performance and accurateness of *cuBLAS* matrix multiplication method. As the reference point they used analogous algorithm from *Intel Matrix Kernel Library* and *ATLAS BLAS*. The experiments were carried out on computer equipped with *NVidia Tesla T10* and 8 core

29

*Intel Xenon Nehalem.* As results show GPU approach significantly outperforms CPU approach when single precision floating point numbers were considered. For double precision both solutions were equally effective. The disadvantage of *cuBLAS* method was, however, slightly smaller accurateness of results.

In [41] problem of WZ Factorization was considered. Authors evaluated the performance of matrix factorization algorithm implemented using CUDA library by comparing it to custom CPU and standard CPU BLAS version WZ factorization algorithm. In their work they used methods from level 1 and level 3 *cuBLAS* library. Experiment was carried out on *NVidia Tesla C2050*. Results show that algorithm written in CUDA outperforms CPU algorithms even by 6 times for large matrices. Authors also point out that CUDA algorithm reached almost 20 times bigger performance expressed in *Gflops*.

*CuBLAS* library was used in [42] to accelerate adaptive Finite Element framework for BLT. The BLT is a sensitive and accurate probing method that uses certain enzymes to mark biological entities like tumor cells or compounds of drugs. As a result in biochemical reaction part of energy is transformed into bioluminescent light which can be monitored. Obtained readings may be processed using FE method can be used to recover 3D image. FE simulation is time consuming process therefore authors decided to redesign their FE application to use *cuBLAS* library to obtain better performance. Experiments were conducted on *NVidia GT240* and results were compared to results obtained from CPU version of FE application executed on machine equipped with 8 core *Intel Xeon*. Research showed that FE application that used *cuBLAS* executed matrix inversion 20 times faster and matrix multiplication over 200 times faster than CPU version of FE application.

30

*Thrust* library was used in research presented in [43] where authors used *Thrust* data structures to search the effective variable-length string sorting algorithm. As they mentioned string sorting was a major issue even when fixed-length strings were used. Algorithm that were proposed simplifies the variable-length string sorting problem to series of short fixed-length string sorting problems: first CPU extract few character long prefixes, second *Thrust* data structure sort operator is used to sort an array of extracted prefixes. Experiments were carried out on *NVidia GTX 580* and *NVidia K20*. On both devices algorithm obtained much shorter execution time than the serial version of the same algorithm. Surprisingly the difference in execution time between *NVidia K20* and *NVidia GTX 580* was not significant, however authors did not covered this case.

In [44] *Thrust* library was used in Discrete Event Simulation – a technique that allows to study the dynamic behavior of complex systems – problem. Authors used a node of supercomputer located in Ohio Supercomputing Center that is built on two *Intel Xeon* cores and *NVidia Tesla M2070*. Similar to other researches in which CPU and GPU versions of the same algorithm are compared when problem scales in small both version has similar effectiveness or CPU slightly outperforms GPU. When the problem scale got larger the execution time of CPU algorithm starts to grow rapidly. Authors observed that CUDA algorithm was almost 60 times faster that its competitor for a large scale problem.

Data structures from *Thrust* library were also used in [45]. Author explored how *Thrust* library can be used to enhance performance of sound simulation and jitter analysis algorithms with minimal changes in already existing serial C++ application. In the experiment machine equipped with *NVidia GTX 480* GPU was used whereas *Intel Core2*

*Quad* CPU was used to generate the reference point results. As the results show GPU approach allowed to obtain better performance for each considered input. For the smallest input data set (1 Million of samples) GPU enabled algorithm was 2 times faster than CPU algorithm; for the largest data set (16 Million of samples) GPU version was over 9 times faster.

# Chapter 2 Examined approaches

Chapter 2.1. Pure GPU approach

*LibMesh* is FE Library and parallel computational framework. It can be run in parallel on thousands CPU cores thanks to it architecture, optimized code, employed MPI, and other functionalities that support parallel execution. Currently *libMesh*, as a part of *MOOSE Multiphysics*, is run on over 20 thousands cores at Idaho National Laboratory [10]. Furthermore it was shown that the applications scales incredibly well. Consequently the first approach to port *libMesh* to GPU assumed that one-to-one translation from CPU thread to CUDA thread will be kept – as such flow of each single GPU thread would be exactly the same as flow of CPU thread in original approach. Perspectives for this approach were extraordinary since even a single GPU would be able to handle hundreds thousands of threads, at cost of lower single thread performance of course, compared to just dozens thousands of threads currently used.

In the first iteration top-to-bottom approach of redesigning was employed. The selected starting point was *libMesh::ParallelObject* class. This effort approached several

issues soon after immediate children were considered. First of all CUDA<sup>2</sup> does not fully support class inheritance and polymorphism. In order to make member function accessible by GPU it has to be at least properly annotated; in certain cases it has to be also reimplemented to match mechanisms supported by CUDA. The problem is possible to solve however it would result in more complicated and less readable code. Furthermore some children classes, like *libMesh::System* and *libMesh::MeshBase*, have pointer based member variables; when such objects are passed to GPU memory, the member pointer still points to host memory. Since GPU operates on different memory address space each reference to pointer variable that points to host memory results in runtime error. To solve that problem all pointer member variables would have to be copied to GPU memory. Additional data transfers impact the performance, not to mention significant additional effort to provide implementation of hundreds post-allocation methods unique to each class with pointer-based member variables. Finally libMesh is highly object oriented application and therefore most of immediate children classes of libMesh::ParallelObject are also parent classes. A common practice in such scenario is to use so called virtual methods. These methods are not defined for parent classes since parent class may be too generic to implement any legitimate functionality of some methods. Children classes are more specialized and therefore supply some functionality related to these methods. This design pattern works great on CPUs but is not supported by GPUs and therefore code cannot be ported without complete redesign of library which is complicated using top-to-bottom approach.

<sup>&</sup>lt;sup>2</sup> as of December 2012 – May 2013

Observations form first iteration led to conclusion that bottom-to-top design tactic may be more beneficial. This iteration started with *libMesh::Parallel::Sort* class. Unfortunately this time also major issues were encountered. Examined class, as well as many of libMesh objects, uses data containers from STL library. STL is a famous C++ library that provides wide selection of data structures with associated very efficient manipulation methods. Library is highly optimized and easy to use therefore it is crucial element in many C++ projects. Unfortunately CUDA does not support STL. In order to solve that issue the content of container would have to be copied to traditional array and then passed to GPU; result returned by GPU would be a classic array also, so content would have to be populate in STL container again. Another issue faced in this iteration was the frequency of branch statements in libMesh code. As mentioned in Chapter 1, GPU executes kernels in SIMT mode. It means that when even thread follows different and "longer" execution path, other threads are forced to stall until the next instruction common for all of them is reached. Although both of these issues are not critical to porting process, the performance of final result would be disappointing and most likely worse that the original one.

Although both design methodologies assessed in this chapter failed, it does not prove that one-to-one translation from CPU thread to GPU thread is impossible. It would require to completely redesign the library architecture and therefore enormous amount of time and work, which exceed the scope of this dissertation and capabilities of one person, would be needed. It is likely that Conversation with Cody Permann – one of *MOOSE Multiphysics* developers – seems to prove the observations. Moreover, significant change like that would result in altering existing API and therefore applications build atop of *libMesh* would have to be modified. Because of that different porting idea, unfortunately less sophisticated, was proposed.

## Chapter 2.2. Hybrid GPU/CPU approach

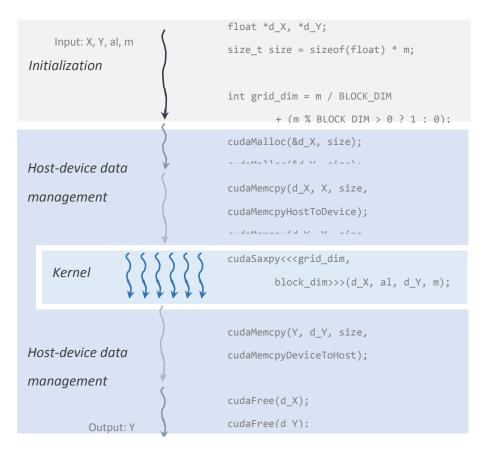

Second approach takes a step back from idea of enclosing very complex algorithms and complex data structures and turns to basic concepts behind GPGPU. CPU and GPU works in a host – device manner. It means that every GPU-enabled application is initialized and handled by CPU. CPU thread or threads follows a normal flow of application and periodically, when some part of algorithm is highly parallel, invokes a GPU kernels that execute selected operation in parallel. Figure 6 presents an example flow of program that performs SAXPY operation.

As it can be seen application starts with a single CPU thread initializes basic parameters and allocates necessary memory. Next CPU thread invokes GPU kernel that fills data structures with data which is later used to perform SAXPY operation. At the end CPU thread displays generated input and result of vector-scalar multiplication. It can be seen that kernels are intended to by highly specialized operation that produces a single element which is a part of bigger result. In serial application kernel would be the operation that is executed within a loop or block of nested loops. This encourages to use this approach to alter libMesh. In [10] it was showed that one of the most time consuming operations are basic linear algebra operations like matrix multiplication or vector addition – all of them executed by CPU in series using multiply nested loops. This approach would, basically, introduce another level of parallelism. Currently simulation starts with a single CPU thread

Figure 6. Standard CUDA program flow

that initializes simulation, set all required parameters, and spawns required number of child threads that executes simulation process in parallel. Finally parent gathers the results from child threads and produces the output. In the new approach child threads will have capability of invoking CUDA kernels in order to execute heavy parallel tasks – like BLAS operations – by GPU. In theory this concept may result in enhanced performance of overall multiphysics simulator, since the most time consuming part of simulation will be improved. Nonetheless it is important to remember that effectiveness of kernel depends on two factors: overhead related to data allocation and quality and level of parallelism of kernel.

Allocating and populating data structures in GPU memory is not an instant and resource-free operation. Therefore it is an overhead that has to be considered when comparing the execution time of CPU and GPU versions of the same operation. Kernel itself is a single operation, in this example generating and multiplying of floating point number, that are executed in parallel by GPU and in series (e.g. in a loop) by CPU. Depending on how time consuming is the operation and on how many operations have to be executed parallel approach can be more or less efficient. Because of that detailed evaluation of all implemented CUDA algorithm is required.

## Chapter 2.3. CUDA 6.5 enhanced hybrid GPU/CPU approach

On August 2014 *NVidia* has released new CUDA programming model versioned with 6.5. Among number of improvements, like new code profiler and extended support to other programming languages, the most significant for research performed in this dissertation was including two libraries, namely *Thrust* and *cuBLAS*, to standard CUDA release. As mentioned in Chapter 1, *Thrust* library is GPU-enabled substitute of STL and *cuBLAS* is GPU version of BLAS. Both, as documentation and research done in this area, are very efficient and stabile libraries. Therefore it was reasonable to assess the performance of these libraries and decide on their usability in multiphysics simulation.

This approach is very similar to the one presented in previous subchapter: heavy computational and highly-parallel algebraic operators were replaced by *cuBLAS* operators in an analogous way they were replaced by custom operators presented in Chapter 2.1.

Complete list of used *cuBLAS* methods together with description of notions they use is presented in Algorithms chapter.

New feature of third approach to redesign *libMesh* is presence of *Thread* library. LibMesh relies heavily on STL containers and Thrust library extends the functionality of STL. The naming convention and majority of object and method names were kept in *Thrust* library. It allows to easily switch from one library to another simply by changing declaration of variable from STL container to Thrust container. New library provides also parallel execution on GPU of certain primitives related to container, like search and sort. It may be very beneficial for overall performance of *libMesh* because it operates on some container primitives. Thrust offers also possibility to access containers stored on GPU directly. It is very likely that host operations on data in GPU memory would be followed by the overhead related to data transfers over PCIe port, however there are cases when it may be irrelevant. When a container is frequently processed by GPU and rarely accessed by CPU then the overhead of retrieving data from GPU memory may be marginal when compared to overhead of frequent allocation from host to GPU memory. Potential improvements appeared to be so promising that in this approach each occurrence of STL library was replaced by corresponding container from *Thrust* library.

## Chapter 2.4. Limitations

GPGPU was invented with intention to speed up processing in research facilities equipped with HPC. Obviously one GPU, even from the cutting-edge segment, would be unable to replace thousands of high-performance modes that consist of number of modern CPU. Therefore graphic cards has to be used "in bulk". This exposes engineers to several hardware design problems that hast to be overcome in order to provide not only better performance but also comparable fault-tolerance, resilience, and survivability of already existing classic high-performance clusters.

HPC systems keep scaling in volume together with more and more complex computations they perform. It is also accompanied, unfortunately, with escalation of failure frequency which may forfeit hours of computing of long-running applications. In classic supercomputer environments so called checkpoint/restart technique is used. The idea is to periodically save a state of execution on one or more reliable storage systems and in case of failure restore it and resume a normal flow. When classic CPU system is considered checkpoint/restart mechanism can be accomplished at three levels: kernel, library and application levels [46]. At kernel level the operating system, like *V-System* [47] or Charlotte [48], can spawn a process transparent to developer that can construct the state. At the library level library itself is responsible for providing checkpoint/recovery functionality. One of the examples is *Berkeley Lab Checkpoint/Restart* library which uses system calls to save registers content onto the stack [49]. Finally when the checkpointing and restarting mechanism is delivered at application level then developers need to implement such functionality into their product [50].

## Chapter 3 Algorithms

## Chapter 3.1. Proposed algorithms

#### a. Memory Allocation

CUDA framework offers various methods that allocate memory in device and pass data between host and device. Some of them are just wrapper functions around original CUDA allocation and transmission methods, other offers preprocessing steps or align data in memory to maximize performance of kernel. As it can be seen first memory is allocated using *cudaMalloc*, then one can copy specified amount of data from host memory (pointed by pointer to host memory) to device memory (pointed by pointer to device memory). At the end device memory is released using *cudaFree* method.

*CuBLAS* library offers its own methods that handle data allocation. Basically these method are just a wrapper functions that eventually uses standard *cudaMalloc*. However the advantage of *cuBLAS* methods is that data can be preprocessed before it is transferred to device. Thanks to the preprocessing user may for example transpose matrix before passing it to GPU within one method call.

The last considered method of handling the memory comes from *Thrust* library. The undisputed advantage of this approach is flexibility. Developer does not have to remember to manually allocate the memory and copy data because everything is done by simply assigning *thrust::host\_vector* to *thrust::device\_vector*. This functionality simplifies the process of developing and refactoring existing code.

b. AXPY

Level 1 of every BLAS library is reserved for vector operations like dot product or vector norms. In this research a classic AXPY operation – which is a simple vector-scalar multiplication summed with second vector – is considered. Operator is defined as  $y = \alpha x + y$  where  $\alpha$  is a scalar, x and y are vectors of equal dimension.

In standard CPU approach, presented in Algorithm 1, for every loop iteration equation (4) is calculated. Complexity of this algorithm is O(n).

$$y[i] = \alpha \cdot x[i] + y[i] \tag{4}$$

Second considered algorithm was implemented in plain CUDA and is presented in Algorithm 2. Each element of output vector y is calculated by a single GPU thread so that *i*-th element is calculated by a thread given by *threadIdx.x* and *blockIdx.x* where  $i = threadIdx.x + blockIdx.x \cdot blockDim.x$  using formula (4). Complexity of this algorithm, assuming parallel execution, is O(1).

#### c. Vector Swap

Swap operator, also included in level 1 of BLAS library, switches the places of corresponding elements in two vectors. In CPU approach each pair of elements would be swapped in a single loop (Algorithm 3) using procedure (5). The complexity of this algorithm is O(n).

$$v = y[i] \to y[i] = x[i] \to x[i] = v \tag{5}$$

CUDA equivalent of swap operator in presented in Algorithm 4. A grid of threads, equal in size to vectors, is overlaid on vectors and each GPU thread swaps a pair of elements from input vectors: *i*-th element is swapped using formula (5) by thread *threadIdx.x* and *blockIdx.x* where  $i = threadIdx.x + blockIdx.x \cdot blockDim.x$ Complexity of this parallel algorithm is O(1).

#### d. Vector Addition and Vector-Scalar Multiplication

In the simulation process very often a special cases of AXPY operator are used. Two of them are sum of two vectors and vector-matrix multiplication. Although the same result can be obtained using AXPY, this two operators perform twice less floating point operations and therefore is, in theory, twice faster. The output of vector-vector addition is defined by y = x + y. Serial approach performs the operation in a single loop; each iteration performs following operation (6). Scalar-vector multiplication is also executed in one loop; in each iteration (7). Algorithms are presented by Algorithm 5 and Algorithm 7. Complexity of both operators is O(n).

$$y[i] = x[i] + y[i]$$

(6)

$$y[i] = \alpha \cdot y[i] \tag{7}$$

In corresponding GPU version of vector addition and vector-scalar multiplication, presented in Algorithm 6 and Algorithm 8 respectively. Each thread performs the same operation as single iteration of corresponding CPU algorithm; *i*-th element is calculated by thread *threadIdx*. x + blockIdx.  $x \cdot blockDim$ . x. Complexity of these algorithms is O(1).

e. DOT Product

Another operator frequently used by FE libraries is DOT Product operation. DOT operator is here understand in algebraic manner. Operator takes two vectors and calculates sum of multiplied corresponding elements. Result is given by formula (8). CPU algorithm executes the operation in a loop in which it takes two corresponding elements from input vectors, multiplies them, and increment the result (Algorithm 9). Complexity of this algorithm is O(n).

$$d = \sum_{i=1}^{n} x[i] \cdot y[i] \tag{8}$$

CUDA version of DOT Product is a little bit less straightforward. To calculate the result of DOT Product is necessary to traverse entire vector, therefore it is highly serial execution scenario; GPUs does not handle this type of problems, called gather operation, very well since parallel execution is rather enforced that applied. It is, however, possible to distribute the work among threads – in this case each thread will calculate multiplication

result of a single pair of element so that *i*-th pair will be processed by thread *threadIdx*. x + blockIdx.  $x \cdot blockDim$ . x. After that threads will atomically add the results to variable that will represent DOT Product value. Algorithm is presented in Algorithm 10; complexity of this algorithm, assuming parallel execution, is O(1).

#### f. GEMV

Level 2 of BLAS library is responsible for matrix-vector operations including matrix-vector multiplication operator (GEMV) defined as  $y = \alpha Ax + \beta y$ . Serial GEMV (Algorithm 11) operator performs multiplication in doubly nested loop, therefore complexity of this algorithm is  $O(n^2)$ . Each iteration of outer loop is responsible calculating single element of output vector using (9) where sigma sign represents inner loop.

$$y[i] = \alpha \sum_{i=1}^{n} (A[i][j] \cdot x[j]) + \beta y[i]$$

(9)